Vol. 23, No. 3, June, 2021, pp. 221-228

Journal homepage: http://iieta.org/journals/ejee

## Design and Analysis of the STATCOM Based on Diode Clamped Multilevel Converter Using Model Predictive Current Control Strategy

Raaed Faleh Hassan, Suha Sabah Shyaa\*

Middle Technical University, Electrical Engineering Technical college, Baghdad 10001, Iraq

Corresponding Author Email: sabahsuha9@gmail.com

| https://doi.org/10.18280/ejee.230306  | ABSTRACT                                                                                   |

|---------------------------------------|--------------------------------------------------------------------------------------------|

| Received: 4 June 2020                 | In recent decades, multi-level converters have become popular and used in many power       |

| Accepted: 16 April 2021               | systems applications. Compared with conventional converters, multi-level converters        |

|                                       | contribute to reducing the voltage stress on the switching devices and enhancing the power |

| Keywords:                             | quality delivered to the load. In this paper, the study of the five-level diode clamped    |

| STATCOM diada clamped converter model | multilevel converter based static synchronous compensator has been accomplished. Model     |

STATCOM, diode clamped converter, model predictive current control, low harmonic distortion

# In recent decades, multi-level converters have become popular and used in many power systems applications. Compared with conventional converters, multi-level converters contribute to reducing the voltage stress on the switching devices and enhancing the power quality delivered to the load. In this paper, the study of the five-level diode clamped multilevel converter based static synchronous compensator has been accomplished. Model Predictive current control strategy which a type of modern control algorithms was employed for driving the proposed compensator. The suggested five level converter controlled by model predictive current control is firstly examined to verify that this control algorithm is appropriate for achieving the desired performance. Then the proposed compensator in distributed power system. Moreover, in order to examine the robustness of this compensator, the load status is suggested to be heavy inductive. Simulation process has been performed using MATLAB – SIMULINK software package. The results show that the implemented configuration (converter and control algorithm) provides high power quality improvement with adequate reactive power compensation.

### **1. INTRODUCTION**

Recently, electrical power enhancement becomes a vital challenge due to the boundless use of the nonlinear loads. These types of loads cause an increase in the reactive power, imposing undesirable current harmonics and producing unbalanced problems onto the system [1]. One of the most important solutions adopted to overcome these challenges is the use of a Flexible AC Transmission System (FACTS). According to the IEEE the FACTS controller is employed to enhance the power quality and boost the ability of the power transfer in the power system based on the controllable injection or absorption of the reactive power. Various configurations of FACTS controller are introduced and between these configurations, the most advanced one is that employs the voltage source converter (VSC) [2]. The voltage source converter will be acts as shunt compensator; in this case it is called static synchronous compensator (STATCOM). It can also act as a series compensator; in this case it is called Synchronous Series Compensator (SSSC). Static Α combination of series and shunt compensation is also available and it is called Unified Power Flow Controller (UPFC) [2]. Between these three types of VSC configurations, the most popular type is the STATCOM configuration. Employing the STATCOM for compensating the distributed power quality of the electrical network has widely spread during the past decades [3]. Most of the STATCOMs devices are configured using step-down transformer, 2-level voltage source converter and filters. This conventional configuration is bulky and costly, also the converter must operate at high switching frequency in order to reduce the harmonic distortion. A configuration that utilizes 3-level converters can generate waveforms with low

harmonics distortion and significant reduction in the switching frequency. This type of configuration combines the converter with a phase shift transformer to produce stair case waveforms at high voltage levels. These types of configurations are costly with high degree of control complexity [4]. Recently, the development of the multi-level converters (MLC) leads to the employing of semiconductor devices in medium and high voltage power systems. Therefore, the substantial feature of using STATCOM based on multi-level converters is the possibility of excluding the interfacing transformers. Also, the MLC provides a lower switching frequency and low harmonics distortion which reduces the power losses and increases the efficiency of the STATCOM [4, 5]. According to these benefits, the configuration of STATCOM using MLC has attracted more attention and become more popular in medium and high voltages applications. The basic configurations of the MLC are Flying-Capacitor MLC (FCMLC), Diode-Clamped MLC (DCMLC) and cascaded H-Bridge MLC (CHMLC) [6]. Diode Clamped Multi-Level Converter (DCMLC) based Static Synchronous Compensator (STATCOM) possess the ability to improve network performance with the ability to deal with medium and high voltages without need of interfacing transformer [6]. Moreover, it is capable to work regularly under unbalanced voltages and currents of the power systems [5]. Furthermore, the increasing of the voltage levels in the converter leads to a significant reduction in the total harmonics distortion (THD) of the line currents. However, there are challenges and difficulties facing the operation of the DCMLC which can be mentioned as possible drawbacks [7]. One of the important challenges related with the design and operation of the 3-phase MLC is the issue of the control strategy, especially for power quality improvement applications, which needs converters that able to ensure fine reduction for voltage distortion and increase power factor [8]. Multiple single input single output (SISO) proportional integral (PI) loops with pulse width modulation (PWM) were massively introduced for driving DCMLC [9], [10]. The major drawback with the PI – PWM strategy is its poor performance when the fast-transient response is needed or during working at low switching frequency [11]. Modern control concept is the promising alternative methods for driving or controlling the multi – input multi – output (MIMO) system such as DCMLC. Model predictive current control (MPCC) is one of the most important modern control techniques developed in the time domain. Recently, enormous achievements were made towards the verification of the MPCC in controlling power converters based on the comparison with the conventional controllers [8]. In ref. [12], a comparison has been made between MPCC and the conventional PWM strategies for controlling 3-level DCMLC. The results show a similar harmonics spectrum in steady state, while the MPCC has lower tracking error. Furthermore, in ref. [13] MPCC accomplished an improved result for output voltage THD compared with the dq-transformation and PI controllers. Also, the results show the robustness of the MPCC to reject the load disturbances compared with the conventional PI controller [13]. The idea behind the MPCC algorithm is to minimizes a predefined cost function which is subject to the progression of the constrained model of the system with manipulated variables during a finite duration of time [14]. According to the finite switching states of the DCMLC facilitates the possibility of achieving optimal actuating state using MPCC in very short period [15, 16].

In this paper MPCC will be employed for driving the 3phase five-level DCMLC firstly as an inverter afterward it will be used for driving the STATCOM based on five-level DCMLC. In this paper, the basic principles of the Diode Clamped Multi-level converter are covered in section 2. The Model Predictive Current Control strategy and the derivation of the discrete-time model of the converter were explained in section 3. The principles of the STATCOM are briefly demonstrated in section 4, while its configuration in power system is explained in section 5. In section 6, the simulation results for the inverter and the STATCOM are presented. Finally, the conclusions are outlined in section 7.

# 2. DIODE CLAMPED MULTI-LEVEL CONVERTER DCMLC

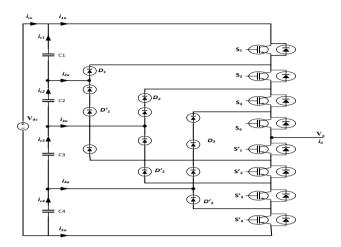

This type of converters has been firstly introduced in 1979 [7] and then it is popularized in 1980's [17, 18], and it is recently considered as the basic structure of the recent multilevel converters [19]. It has been employed for high voltage and high-power applications for many years [20]. For n-level DCMLC, the DC voltage source (V<sub>dc</sub>) is uniformly partitioned into a smaller level through (n -1) series connected capacitors which leads to stepped the output voltage of the converter and limits the voltage stress on the switching device to the V<sub>dc</sub>/(n-1) [19]. Also, DCMLC requires (n-1)  $\times$  (n-2) clamping diodes/ phase with equally voltage ratings [17-19]. As the number of the voltage levels are increased, high quality power delivered to the load is obtained and the load voltage shape becomes closer to the sine waveform [21]. In this paper, 5- level DCMLC (FLDCMLC) is proposed, one leg FLDCMC is shown in Figure 1, the circuit contains of 8-switching devices, 12-clamping diodes and 4-capacitors, C<sub>1</sub>, C<sub>2</sub>, C<sub>3</sub> and C<sub>4</sub>. Suppose that the magnitude of the dc supply voltage is V<sub>dc</sub>, then the voltage through each capacitor is V<sub>dc</sub>/4. Therefore, each power switch voltage stress will be restricted to the level of V<sub>dc</sub>/4 by means of clamping diodes. Table 1 shows the switching states and the corresponding voltages for one leg of the converter.

Figure 1. Structure of Five Level Diode Clamped Multi-Level Converter FLDCMLC

Table 1. Switching states and corresponding voltages of

FLDCMC per leg

| Converter States/leg x |           |           |           |     |     |             | Valtage (V) |                           |

|------------------------|-----------|-----------|-----------|-----|-----|-------------|-------------|---------------------------|

| <b>S1</b>              | <b>S2</b> | <b>S3</b> | <b>S4</b> | S1′ | S2' | <b>S</b> 3′ | S4′         | Voltage (V <sub>x</sub> ) |

| 0                      | 0         | 1         | 1         | 1   | 1   | 0           | 0           | 0                         |

| 0                      | 1         | 1         | 1         | 1   | 0   | 0           | 0           | +Vdc /4                   |

| 1                      | 1         | 1         | 1         | 0   | 0   | 0           | 0           | +Vdc /2                   |

| 0                      | 0         | 0         | 1         | 1   | 1   | 1           | 0           | -Vdc /4                   |

| 0                      | 0         | 0         | 0         | 1   | 1   | 1           | 1           | -Vdc /2                   |

The total switching states of FLDCMC are 125 states, while there are some states are redundant and produce the same voltage vector, therefore the converter can apply 61 different voltage vectors to the load from the total number of switching states [22]. For three-phase applications, the voltage vector produced based on each switching state is determined according to the following equation:

$$v = \frac{2}{3}(v_a + \boldsymbol{a}v_b + \boldsymbol{a}^2 v_c) \tag{1}$$

where, *a* is the complex operator:  $a = e^{j2\pi/3}$ ,  $v_a$ ,  $v_b$  and  $v_c$  are the voltages obtained according to Table 1.

# 3. MODEL PREDICTIVE CURRENT CONTROL STRATEGY

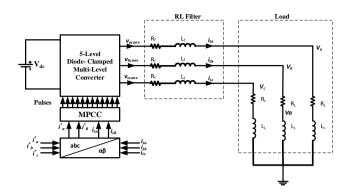

Model predictive current control (MPCC) is a very vast type of control algorithms that is found comparatively recent in the power converters applications. The major feature of MPCC is the investment of the system model to predict the future action of the controlled variables. The control algorithm makes use of this information to produce the optimal actuation pulses based on the predefined index [11, 14, 16, 22]. The MPCC based control of the FLDCMLC which is connected to the 3phase RL load through RL filter is shown in Figure 2. The prediction process is performed for all switching states combinations per sampling interval and the switching state that produce minimum cost function will be delivered to the output at the adjacent sampling period [23].

Figure 2. MPCC based FLDCMLC control

Three phase reference and measured line currents are transformed to the alpha – beta axes using Clarke transformation method which can be described as shown in Eq. (2) below:

$$\begin{bmatrix} i_{\alpha}(t) \\ i_{\beta}(t) \end{bmatrix} = \frac{2}{3} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \end{bmatrix} \begin{bmatrix} i_{a}(t) \\ i_{b}(t) \\ i_{c}(t) \end{bmatrix}$$

(2)

The differential equation at the load side of the circuit is obtained using Kirchhoff's voltage law (KVL) as in Eq. (3):

$$v(t) - L_L \frac{di(t)}{dt} - R_L i(t) - e(t) = 0$$

(3)

where, v(t) is the complex form of the converter voltage obtained from Eq. (1), e(t) is the back-emf induced in the load circuit and i(t) is the complex form of the load current which has the following form:

$$i(t) = i_{\alpha}(t) + ji_{\beta}(t) \tag{4}$$

Eq. (3) can be re-arranged as follows:

$$\frac{di(t)}{dt} = \frac{1}{L_L} \left( v(t) - e(t) \right) - \frac{R_L}{L_L} i(t)$$

(5)

The discrete-time form of the load current can be described using 1<sup>st</sup> order forward Euler's equation:

$$\frac{di(t)}{dt} = \frac{i(k+1) - i(k)}{T_s}$$

(6)

where, i(k) is the load current at sample k, i(k + 1) is the load current at sample (k + 1) and  $T_s$  is the sampling interval. Therefore, the resulting discrete-time form of Eq. (4) will be:

$$i^{p}(k+1) = \left(1 - \frac{R_{L}T_{s}}{L_{L}}\right)i(k) + \frac{T_{s}}{L_{L}}\left(v(k) - e^{(k)}\right)$$

(7)

It is clear from Eq. (6) that the future value of the load current can be predicted according to the parameters obtained

at the current sample. The estimated value of the back-emf  $(e^{(k)})$  can be determined from the following equation:

$$e^{(k-1)} = v(k-1) - \left(\frac{L_L}{T_s}\right)i(k) - \left(R_L - \frac{L_L}{T_s}\right)(i(k-1))$$

(8)

The determination of the cost function is described by the following equation:

$$g = \left| i_{\alpha}^{*}(k+1) - i_{\alpha}^{p}(k+1) \right| + \left| i_{\beta}^{*}(k+1) - i_{\beta}^{p}(k+1) \right|$$

(9)

where,  $i_{\alpha}^{*}$  is the real component of reference current,  $i_{\beta}^{*}$  is the imaginary component of the reference current,  $i_{\alpha}^{p}$  is the real component of predicted current and  $i_{\beta}^{p}$  is the imaginary component of predicted current at the adjacent sampling interval (*k*+1). Reference current is obtained from outer loop and the load current at sample interval (*k*) is measured, then the model will estimate the value of load current at (*k*+1) for each switching state (voltage vector), and the cost function is determined.

The flow chart shown in Figure 3 summarize the MPCC algorithm for controlling the FLDCMC [24]:

Figure 3. Flow chart of MPCC for FLDCMLC

The initial conditions are the state of the converter and the cost function. The state of the converter which produces zero output voltage was taken as the starting point for each sampling interval. Moreover, for each sampling interval the cost function is assumed to be infinity to guarantees the convergence to the minimum value.

### 4. STATCOM PRINCIPLES

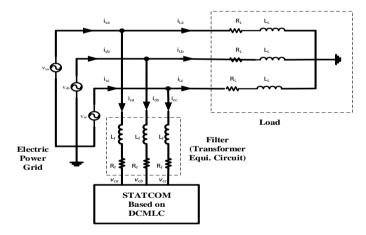

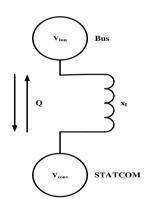

STATCOM is a power electronics voltage source converter employed to inject or absorb reactive power into the electrical grid. It is a member of Flexible AC Transmission System (FACTS) family shunt devices [25]. Figure 4 shows the basic connection of the STATCOM to the electric power grid through step-down transformer which is replaced by its equivalent circuit and as an RL filter. The STATCOM block contains the FLDCMLC and MPCC that explained previously in Figure 2, the DC source is eliminated in this case. The principles of the reactive power exchange between STATCOM and the grid is illustrated in Figure 5. At steady state  $V_{bus} = V_{conv}$  and no reactive power (Q) exchange will occur, when the  $V_{bus} > V_{conv}$  the reactive power (Q) will flow from Bus to the STATCOM (absorption) and when the  $V_{bus}$  < V<sub>conv</sub> then the reactive power (Q) will flow from STATCOM to the Bus (injection). The exchanging process can be described by the following equation [25]:

$$Q = \frac{V_{conv}(V_{conv} - V_{bus})}{X_f}$$

(10)

The differential equation at the AC side of the circuit of Figure 4 is obtained using Kirchhoff's voltage law (KVL):

$$v_s(t) - L_f \frac{di_c(t)}{dt} - R_f i_c(t) - v_c(t) = 0$$

(11)

Figure 4. Basic connection of STATCOM

where,  $v_s(t)$  is the bus voltage in complex form  $(v_{s\alpha}(t))$  and  $v_{c\beta}(t)$  and  $v_c(t)$  is the STATCOM voltage in complex form according to Eq. (1). The discrete-time model of Eq. (10) based on 1<sup>st</sup> order Euler's equation will be:

$$i_{c}^{p}(k+1) = \frac{T_{s}}{L_{f}} \left( v_{s}(k) - v_{c}(k) \right) + \left(1 - \frac{R_{f}T_{s}}{L_{f}}\right) i_{c}(k) \quad (12)$$

When it is working with STATCOM, MPCC algorithm will adopt Eq. (12) instead of Eq. (7) and Eq. (8) will be not used.

### 5. STATCOM CONFIGURATION IN POWER SYSTEM:

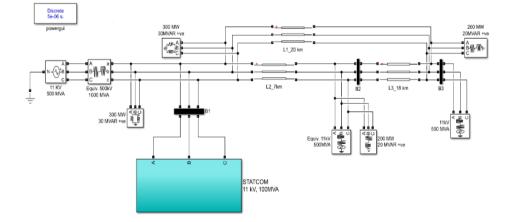

The above – mentioned STATCOM based on FLDCMLC is configured for compensating the power quality delivered to the loads of the distribution power system shown in Figure 6. This power system is connected in a ring manner and its parameters are listed in Table 2 shown below:

Table 2. Distribution power system parameters

| Description of Parameters | Rating          |

|---------------------------|-----------------|

| Rated voltage             | 11 KV           |

| Base voltage              | 11 KV           |

| Frequency                 | 50 Hz           |

| S.C level                 | 500 MVAR        |

| Load 1                    | 300 MW, 30 MVAR |

| Load 2                    | 300 MW, 30 MVAR |

| Load 3                    | 200 MW, 20 MVAR |

| Load 4                    | 200 MW, 20 MVAR |

|                           |                 |

Figure 5. Principles of STATCOM operation

Figure 6. STATCOM based on FLDCMC

### 6. SIMULATION RESULTS

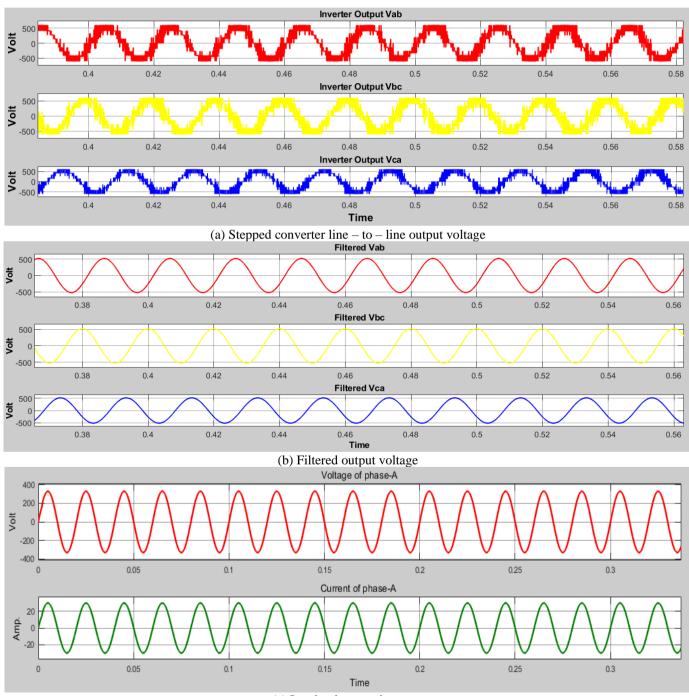

The performance of the proposed five-level inverter (FLDCMLC) and the STATCOM based on FLDCMLDC have been examined by simulation using MATLAB / SIMULINK software package. The simulation of the five-level inverter is carried out based on Figure 2 and the parameters listed in Table 3.

Simulation results of the FLDCMLC is shown in Figure 7. It is clear from these results that the requirements for high quality and low distortion of the power system for load demands have been achieved. Figure 7(a) shows a three-phase line-to-line output voltage of the inverter with Total Harmonic Distortion (THD) of 18.1%. A very low THD (0.48%) is obtained of the filtered three-phase line-to-line output voltage as shown in Figure 7(b). Figure 7(c) shows the line-to-neutral

load voltage and load current with THD of 0.59% for both. Also, it can be noticed that the power factor is very close to unity.

| <b>Description of Parameters</b> | Rating               |

|----------------------------------|----------------------|

| NO. of switches / arm            | 8                    |

| Dc Capacitor                     | 10 mF                |

| DC-Link voltage                  | 500 V                |

| frequency                        | 50 Hz                |

| Phase voltage peak value         | 480 V                |

| Filter inductor                  | 22 mH                |

| Filter capacitor                 | 500 μF               |

| RL load / Phase                  | 18 $\Omega$ and 1 mH |

<sup>(</sup>c) Load voltage and current

|                              |   |     | nv         | nes_Vref (P.U)                                                                                                  | 1 | Т   |   |

|------------------------------|---|-----|------------|-----------------------------------------------------------------------------------------------------------------|---|-----|---|

| 1                            |   |     |            | en allanda eta dalera degla |   |     |   |

|                              | 0 | 1 2 | 2          | 3<br>3lqref (P.U)                                                                                               | 4 | 5 ( | 6 |

| 0.2                          |   |     | N          |                                                                                                                 |   |     |   |

| -0.2<br>-0.4<br>-0.6<br>-0.8 |   |     |            |                                                                                                                 |   |     |   |

|                              | 0 | 1 2 | 2          | 3                                                                                                               | 4 | 5   | 6 |

|                              |   |     |            | PO.                                                                                                             |   |     |   |

|                              |   |     |            | PQ                                                                                                              | 1 | Т   |   |

| 150                          |   |     |            | Pq                                                                                                              |   |     |   |

| 100                          |   |     |            |                                                                                                                 |   |     |   |

|                              |   |     |            |                                                                                                                 |   |     |   |

| 100                          |   | 1   | 2          | 7 <b>U</b>                                                                                                      | 4 | 5   | 6 |

| 100<br>50<br>0               | 0 | 1   | 2 : :<br>D | PQ<br>3                                                                                                         | 4 | 5 ( | 6 |

| 100<br>50<br>0               |   | 1   | 2 :<br>D   | 3                                                                                                               | 4 | 5 ( | 6 |

| 100<br>50<br>0               |   | 1   | 2 :<br>D   | 3                                                                                                               | 4 | 5 ( | 6 |

| 100<br>50<br>0               |   |     | 2<br>D     | 3                                                                                                               | 4 | 5 0 | 6 |

(d) Capacitor Voltages

Figure 8. STATCOM performance

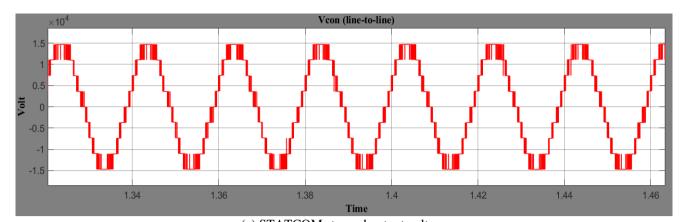

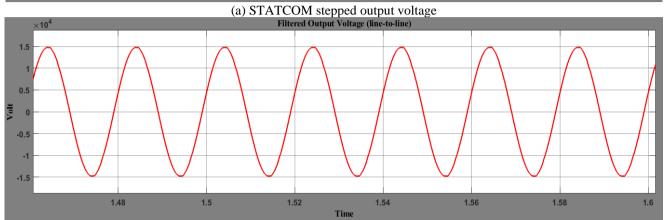

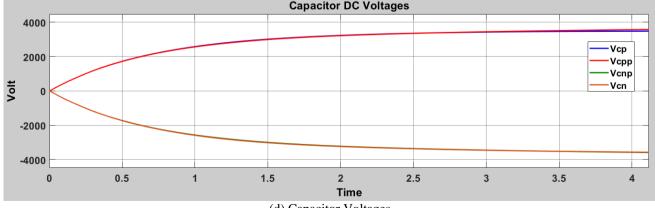

For STATCOM based on FLDCMLC the simulation process is performed based on Table 1 and Figure 6, the results obtained are shown in Figure 8, a stepped output voltage has been acquired from the STATCOM as indicated in Figure 8(a) with acceptable THD (15.2%). The STATCOM supplied a filtered output voltage to the grid with a significant reduction in THD (0.3%) as shown in Figure 8(b). The compensation performance of the suggested STATCOM is verified as shown in Figure 8(c). The top part of Figure 8(c) shows the output voltage response of the STATCOM in p.u. The second part of this figure displays the compensation process of the quadrature component (Iq) of the output current compared with reference one. The reactive power compensation process was appeared in the third part of Figure 8(c), and the angle difference (delta) between the grid voltage and STATCOM voltage is shown bottom part of this figure. A balance voltage across the capacitors of the STATCOM are shown in Figure 8(d), it can be noticed that the DC voltage is divided evenly across the capacitors.

### 7. CONCLUSION

This paper study the operation of the five-level Diode Clamped multi-level converter as an inverter for driving inductive load and as a STATCOM for compensating the voltage at the electrical distribution system. Model Predictive Current Control strategy was adopted for controlling the STATCOM. Simulation results show that the five-level Diode Clamped multi-level inverter supplies a high-quality ac power by means of a significant reduction in the Total Harmonic Distortion (THD) with a close to unity power factor. The stepped form of the output voltage of the inverter indicates the possibility of constraining the voltages across the devices. Therefore, multi-level converter configurations permit of using switching devices in the higher voltages' ratings. These encouraging results have made the use of multi-level converters to work as STATCOM. The STATCOM based on the FLDCMLC was adopted for compensating the power quality of the electrical power distribution system. The performance of the proposed STATCOM was examined by simulation and the results show the fast response of the STATCOM to compensate the power quality of the grid. Adoption of the model predictive current control for controlling the converter and the STATCOM significantly simplified the control structure and calculations. This control strategy provides a fast response with maintaining a high quality of the load voltages and currents.

### REFERENCES

- Pirouz, H.M., Bina, M.T. (2009). New transformerless STATCOM topology for compensating unbalanced medium-voltage loads. In 2009 13th European Conference on Power Electronics and Applications, pp. 1-9.

- [2] Adepoju, G.A., Komolafe, O.A. (2011). Analysis and modelling of static synchronous compensator (STATCOM): A comparison of power injection and current injection models in power flow study. International Journal of Advanced Science and Technology, 36(2): 65-76.

- [3] Nwobu, C.J., Efika, I.B., Oghorada, O.K., Zhang, L.

(2015). A modular multilevel flying capacitor converterbased STATCOM for reactive power control in distribution systems. In 2015 17th European Conference on Power Electronics and Applications (EPE'15 ECCE-Europe), pp. 1-9. https://doi.org/10.1109/EPE.2015.7309085

- [4] Soto, D., Green, T.C. (2002). A comparison of high-power converter topologies for the implementation of FACTS controllers. IEEE Transactions on Industrial Electronics, 49(5): 1072-1080. https://doi.org/10.1109/TIE.2002.803217

- [5] Mohammadi, P.H., Bina, M.T. (2010). A transformerless medium-voltage STATCOM topology based on extended modular multilevel converters. IEEE Transactions on Power Electronics, 26(5): 1534-1545. https://doi.org/10.1109/TPEL.2010.2085088

- [6] Liu, X., Lv, J., Gao, C., Chen, Z., Chen, S. (2016). A novel STATCOM based on diode-clamped modular multilevel converters. IEEE Transactions on Power Electronics, 32(8): 5964-5977. https://doi.org/10.1109/TPEL.2016.2616495

- [7] Leon, J.I., Vazquez, S., Franquelo, L.G. (2017). Multilevel converters: Control and modulation techniques for their operation and industrial applications. Proceedings of the IEEE, 105(11): 2066-2081. https://doi.org/10.1109/JPROC.2017.2726583

- [8] Rodriguez, J., Kazmierkowski, M.P., Espinoza, J.R., Zanchetta, P., Abu-Rub, H., Young, H.A., Rojas, C.A. (2012). State of the art of finite control set model predictive control in power electronics. IEEE Transactions on Industrial Informatics, 9(2): 1003-1016. https://doi.org/10.1109/TII.2012.2221469

- [9] Antonopoulos, A., Angquist, L., Nee, H.P. (2009). On dynamics and voltage control of the modular multilevel converter. In 2009 13th European Conference on Power Electronics and Applications, pp. 1-10.

- [10] Hagiwara, M., Akagi, H. (2009). Control and experiment of pulse width-modulated modular multilevel converters. IEEE Transactions on Power Electronics, 24(7): 1737-1746. https://doi.org/10.1109/TPEL.2009.2014236

- [11] Geyer, T., Darivianakis, G., Van Der Merwe, W. (2015). Model predictive control of a STATCOM based on a modular multilevel converter in delta configuration. In 2015 17th European Conference on Power Electronics and Applications (EPE'15 ECCE-Europe), pp. 1-10. https://doi.org/10.1109/EPE.2015.7309148

- [12] Aurtenechea, S., Rodriguez, M.A., Oyarbide, E., Torrealday, J.R. (2007). Predictive direct power control of MV-grid-connected two-level and, three-level NPC converters: experimental results. In 2007 European Conference on Power Electronics and Applications, pp. 1-10. https://doi.org/10.1109/EPE.2007.4417305

- [13] Barros, J.D., Silva, J.F. (2009). Multilevel optimal predictive dynamic voltage restorer. IEEE Transactions on Industrial Electronics, 57(8): 2747-2760. https://doi.org/10.1109/TIE.2009.2034172

- [14] Cortés, P., Kazmierkowski, M.P., Kennel, R.M., Quevedo, D.E., Rodríguez, J. (2008). Predictive control in power electronics and drives. IEEE Transactions on Industrial Electronics, 55(12): 4312-4324. https://doi.org/10.1109/TIE.2008.2007480

- [15] Rodriguez, J., Pontt, J., Cortés, P., Vargas, R. (2005).

Predictive control of a three-phase neutral point clamped inverter. In 2005 IEEE 36th Power Electronics

Specialists Conference, pp. 1364-1369. https://doi.org/10.1109/PESC.2005.1581807

- [16] Vazquez, S., Leon, J.I., Franquelo, L.G., Rodriguez, J., Young, H.A., Marquez, A., Zanchetta, P. (2014). Model predictive control: A review of its applications in power electronics. IEEE Industrial Electronics Magazine, 8(1): 16-31. https://doi.org/10.1109/MIE.2013.2290138

- [17] Cho, G.H. (1991). A general circuit topology of multilevel inverter. PESC '91 Record 22nd Annual IEEE Power Electronics Specialists Conference, Cambridge, MA, USA.

- [18] Kim, Y.S., Seo, B.S., Hyun, D.S. (1993). A novel structure of multi-level high voltage source inverter. In 1993 Fifth European Conference on Power Electronics and Applications, pp. 132-137. https://doi.org/10.1109/TENCON.1993.320692

- [19] Raj, P.H., Maswood, A.I., Ooi, G.H., Lim, Z. (2015). Voltage balancing technique in a space vector modulated 5-level multiple-pole multilevel diode clamped inverter. IET Power Electronics, 8(7): 1263-1272. https://doi.org/10.1049/iet-pel.2014.0747

- [20] Khajehoddin, S.A., Bakhshai, A., Jain, P.K. (2006). Modeling and analysis of 5-level diode-clamped and flying-capacitors converters. In 2006 IEEE International Symposium on Industrial Electronics, 2: 1408-1413. https://doi.org/10.1109/ISIE.2006.295678

- [21] Dhal, P.K., Rajan, C.C.A. (2015). Design and comparative analysis of diode clamped multilevel inverter for eliminating total harmonics using high switching frequency techniques. In Power Electronics and Renewable Energy Systems, 665-677. https://doi.org/10.1007/978-81-322-2119-7\_65

- [22] Kieferndorf, F., Karamanakos, P., Bader, P., Oikonomou, N., Geyer, T. (2012). Model predictive control of the internal voltages of a five-level active neutral point clamped converter. In 2012 IEEE Energy Conversion Congress and Exposition (ECCE), pp. 1676-1683. https://doi.org/10.1109/ECCE.2012.6342611

- [23] Hassan, R.F. (2018). Design and software implementation of solid state transformer. International Journal of Engineering & Technology, 7(3): 1776-1782. https://doi.org/10.14419/ijet.v7i3.16423

- [24] Rivera, M., Rodriguez, J., Vazquez, S. (2016). Predictive control in power converters and electrical drives-Part i. IEEE Transactions on Industrial Electronics, 63(6): 3834-3836. https://doi.org/10.1109/TIE.2016.2549498

- [25] Ali, H., Rahardjo, A., Setiawan, A., Jufri, F.H., Husnayain, F. (2019). Voltage profile improvement analysis during the loss of transmission lines on 150kv subsystem using static synchronous compensator. In IOP Conference Series: Materials Science and Engineering, 673(1): 012066. https://doi.org/10.1088/1757-899X/673/1/012066

### NOMENCLATURE

- a Complex operator  $e^{j2\pi/3}$

- *e*<sup>^</sup> Estimated back emf

- g Cost function

- i Measured current, Amp

- *i*<sup>\*</sup> Reference current, Amp

- *i<sup>p</sup>* Predicted current, Amp

- k Current sample

- v Voltage vector, volt

- $v_{a,b,c}$  Three-phase voltages, volt

- Vdc DC voltage applied to the inverter, volt

- x Switching state

### Greek symbols

- $\alpha$  Stationary axis aligned with phase A

- $\beta$  Stationary axis orthogonal with  $\alpha$