# Single phase inverter fed through a regulated SEPIC converter

Adil Hasan Mahmood<sup>1</sup>, Mustafa F. Mohammed<sup>2</sup>, Mohammed Omar<sup>3</sup>, Ali H. Ahmad<sup>4</sup>

<sup>1</sup>University of Information Technology and Communications, Baghdad, Iraq

<sup>2</sup>Renewable Energy Research Center, University of Anbar, Al-Anbar, Iraq

<sup>3</sup>Electrical Engineering Departement, University of Technology, Baghdad, Iraq

<sup>4</sup>Medical Instruments Departement, Al-Hadi Collage, Baghdad, Iraq

## **Article Info**

Article history:

## ABSTRACT

Received Feb 7, 2021 Revised Jun 14, 2021 Accepted Oct 14, 2021

## Keywords:

Converter DC/DC Duty cycle PI-controller SEPIC In power electronics, it is necessary to select the best converter circuit topology that has good performance among different converters. The singleended primary inductor converter (SEPIC) has good performance and is advantageous among different direct DC/DC converters. In this paper, a design of a SEPIC converter is made by selecting the values of its components according to the required output voltage and power. The design is made by an assumption that both of its inductors have the same value. The converter is tested by using MATLAB/Simulink successfully. Later, its output voltage is regulated by using a proportional integral (PI-controller) through tuning its proportional and integral gains. Finally, the SEPIC converter is connected to a single-phase full-bridge inverter to supply its required DC voltage. The role of the SEPIC converter is to regulate the dc-link voltage between its output side and the inverter. The results showed the success of this connection to supply alternating current (AC) loads with low total harmonic distortion (THD).

This is an open access article under the <u>CC BY-SA</u> license.

## Corresponding Author:

Adil Hasan Mahmood University of Information Technology and Communications Baghdad 00964, Iraq Email: adil.hasan@uoanbar.edu.iq

## 1. INTRODUCTION

In power electronics, there are many categories of DC/DC converters that are either stepping up or down or even both for the supplied voltage [1]-[3]. The single-ended primary-inductor converter (SEPIC) is a DC/DC converter that is stepping up or down of its supplied voltage. The circuit is built mainly from 2 inductors, 2 capacitors, and one switch. The switch is either metal oxide semiconductor field effect transistor (MOSFET) or insulated gate bipolar transistor (IGBT). Due to its design, the circuit is able to give output voltage at the same polarity as the supplied voltage [2]-[5]. There are many researchers who made their own design of SEPIC converter. The design may contain coupled or uncoupled inductors [6]. The work that was made by DeNardo et al. [7] is a design of SEPIC converter passive elements which is done by using the acceptability boundary regions (ABR) method. This method determines an area in the space of parameters according to commercial components. The reason behind using this method is to ensure acceptable ripples of voltage to attain maximum allowed power dissipation and non-pulsating source current absorption as well. A normal design and analysis of SEPIC converter for photovoltaic (PV) applications are made and simulated by MATLAB simulation environment but without output voltage regulation [8]. There is an analysis is made for a SEPIC converter with a proportional-integral-derivative (PID) controller to regulate its output voltage by Bhavin et al. [9]. Their system is simulated in matriks laboratory MATLAB/Simulink. Geeta and R. [10] are analyzed the diode part of the SEPIC circuit. They had replaced it with a switch to make better operating by avoiding the discontinuous conduction mode (DCM). This yielded to save the diode inverse voltage. Their

design has a compound PWM technique to ensure the synchronization between two switches. A design of SEPIC boost converter is made by Alhamrouni et al. [11] for PV applications where the converter ensures continuous current and high voltage gain. The circuit design is able to reduce stress on the power switch as well. An extended high gain SEPIC converter for photovoltaic applications is made by Alishah et al. [12]. Their design merges SEPIC converter and switched capacitors. The design provides a constant dc voltage at its output side with tracking the maximum power point tracking (MPPT). A modified SEPIC circuit with and without winding isolation and connected with a three-phase PWM inverter is made by Yadav and Verma [13]. Their system is regulated and simulated via MATLAB/Simulink. A regulation by PID for a SEPIC converter is made by Pathirathne and Maduranga [14]. In their research, the converter design steps and its output voltage regulation are presented in a comprehensive way and the system is simulated by Simulink. The current paper presents a design of a regulated voltage SEPIC DC-DC converter. The converter is connected to a full-bridge inverter to supply AC loads. The role of the SEPIC converter is to regulate the voltage for the dc-link between its output side and the inverter. The paper involves the design of a SEPIC converter, regulating its output voltage, and then connect it to a single-phase full-bridge inverter. This paper is organized as follows: an introduction, analysis of SEPIC converter, design specification, simulation results, regulation of SEPIC converter, connecting SEPIC converter to a full-bridge inverter, and conclusion.

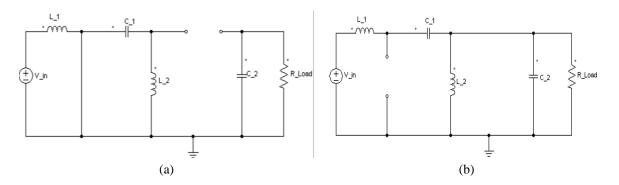

## 2. ANALYSIS & DESIGN OF SEPIC CONVERTER

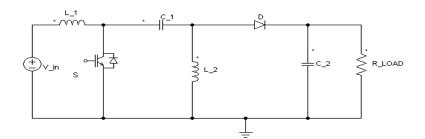

The SEPIC converter contains 2 inductors, 2 capacitors, and 1 switch which are mainly MOSFET or IGBT as shown in Figure 1. There are two modes of operation according to switching conditions. In Figure 2 (a), if the switch S is ON, the inductor  $L_1$  is charging,  $C_1$  is charging the inductor  $L_2$ . In this case, the diode D is reverse biased. In Figure 2 (b), when the switch S is OFF,  $L_1$  is discharging towards  $C_1$  which is currently charging, and  $L_2$  also discharging and D is forward biased [15]-[17].

Figure 1. SEPIC converter circuit

Figure 2. Modes of SEPIC converter operation, (a) mode 1, S is ON, (b) mode 2, S is OFF

The duty cycle is defined as the ratio between the time when S is ON and the whole cycle period. According to the duty cycle of the switch S, the voltages and currents of each component in the circuit are varied. The following mathematical expressions are used to find the value of each of the converter components where an assumption can be made which is the change in input current is 20% of the full load

input current. Another assumption can be made which is the change in  $L_1$  current is similar to the  $L_2$  current change.  $L_1$  and  $L_2$  can be calculated by the following formula:

$$L_1 = \frac{V_{s\min}*D_{max}}{f_s*\Delta I_{L_1}} \tag{1}$$

$$L_2 = \frac{V_{s\min}*D_{max}}{f_s*\Delta I_{L_1}} \tag{2}$$

$f_s$  is known as the switching frequency in Hertz. The maximum duty cycle  $D_{max}$  can be calculated by the following formula:

$$D_{\max} = \frac{V_0 + V_D}{V_0 + V_D + V_{\text{in min}}}$$

(3)

The coupling capacitor C\_2 can be found from the formula:

$$C_{-1} = \frac{I_{Omax} * D_{max}}{\Delta V_1 * f_S} \tag{4}$$

Where  $\Delta V_{in}$  is about 1% of the required input voltage whereas the output capacitor C\_2 value becomes:

$$C_2 = \frac{I_{Omax} * D_{max}}{\Delta V_o * f_S}$$

(5)

$\Delta V_o$  is about 1% of the required output voltage. The maximum output current can be calculated by using the formula:

$$I_{Omax} = \frac{P_{Omax}}{V_O} \tag{6}$$

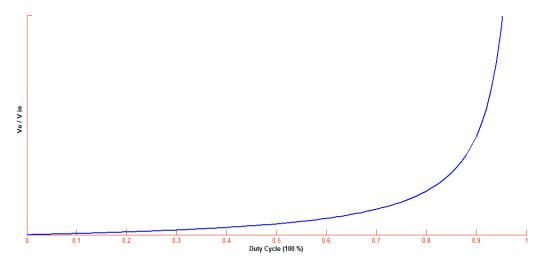

The ration between the V\_in and Vo can be calculated by the following formula and shown in Figure 3.

$$\frac{Vo}{V_{in}} = \frac{D}{(1-D)}$$

(7)

where D is the duty cycle.

Figure 3. SEPIC converter voltage gain (V<sub>o</sub>/V<sub>in</sub>) and its duty cycle (D)

From Figure 3, it can be noted that the best working area when D is less than 90%. And below 50% the voltage change tends to be more linear. When D is 50% then  $Vo \approx V_{in}$ . Acording to the required output power and voltage ranges, and by using the formulas in the previous section of this paper, the SEPIC converter parameters can be calculated and listed in Table 1 where the maximum output power is 2 kW.

| Component | Value/Type  |

|-----------|-------------|

| L_1       | 750 uH      |

| L_2       | 750 uH      |

| C_1       | 200 µF      |

| C_2       | 600 µF      |

| S         | IGBT        |

| V_in      | 100 - 120 V |

| Vo        | 311 V       |

| f.        | 25 kHz      |

Table 1. SEPIC converter components values

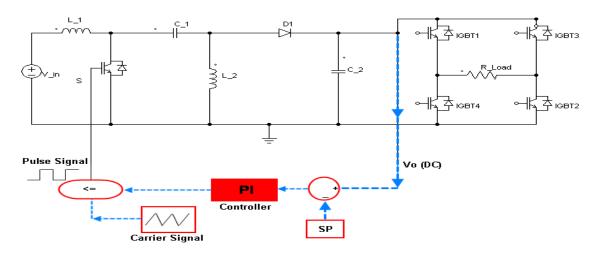

## 3. THE PROPOSED CONVERTERS CONNECTION

In this paper, the proposed connection of the converters is made where the designed SEPIC converter is connected to a full-bridge inverter [18], [19] to supply AC loads as shown in Figure 4. The SEPIC converter with the proportional integral controller (PI-controller) is responsible for fixing the DC voltage that is supplied to the inverter. The role of the SEPIC converter is to supply the required and regulated DC voltage to the input terminals of the inverter. A PI-controller [20], [21] is an efficient controller to regulate the output voltage of the SEPIC converter. The PI-controller is used to regulate the DC-link voltage between the SEPIC converter and the inverter. This voltage regulation aims to get constant DC voltage and to reduce the overshoot effect during load switching. As shown in Figure 4, the voltage signal is from the DC-link is compared with a set point (SP). The result of this comparison is the error that will be fed to the PI-controller. This controller is tuned to get its required proportional and integral gains [22]. The generated control signal is then modulated with a high-frequency carrier signal f\_s to generate the required pulses for the S switching device.

Figure 4. The proposed regulated SEPIC converter connected to single-phase full bridge inverter

## 4. SIMULATION RESULTS

The SEPIC converter of Figure 1 is simulated by using MATLAB/Simulink. The specifications of its components are as listed in Table 1. The simulation is made according to the following steps:

## 4.1. Test of the SEPIC converter individually

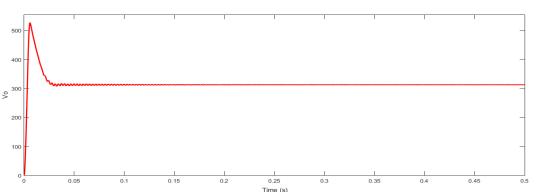

This test is made for SEPIC converter without any voltage regulation. Figure 5 shows the output voltage at starting of the converter. In this figure, it can be noted that the converter has a very fast response but, there is a huge overshoot percentage in the output voltage value which is 73.6% approximately at full load. If the load is decreased, this percentage may be more.

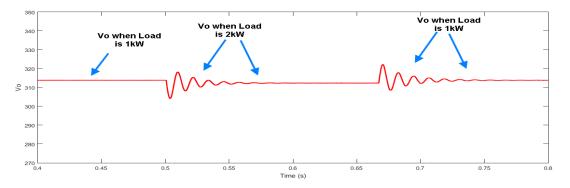

In another way, let's suppose there is a load switching from half load to full load for some period of time and then the load is repeated to be half-load again. This case is shown in Figure 6. It can be noted that there is a voltage dip when the load is increased and voltage swells when the load is decreased. The operation of each load changing is accompanied by voltage fluctuations for some time.

Figure 5. Output voltage of SEPIC converter during starting

Figure 6. Output voltage of SEPIC converter load switching

#### 4.2. Regulation of sepic converter

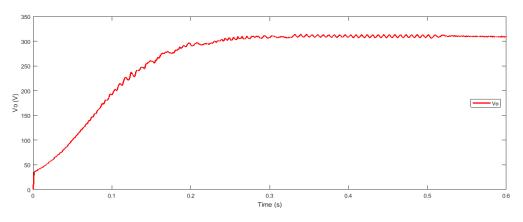

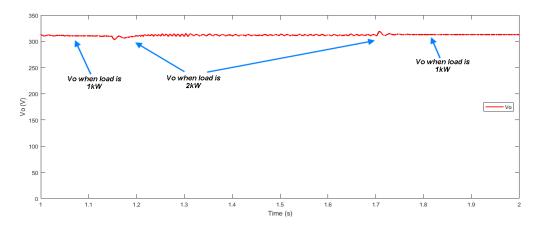

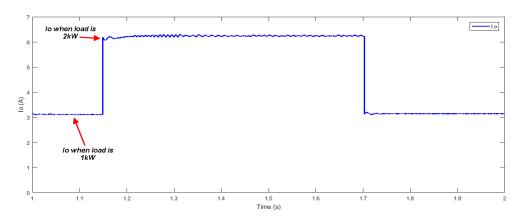

From the voltage results that are shown in Figures 5 and 6, it can be seen that during system starting there is a huge value of overshoot percentage and also there are more voltage fluctuations and decrease in the output voltage value. From these results, it can be concluded that there is a need for regulating the output voltage to absorb the high values of changes or fluctuations. From (7), it can be noted that only the duty cycle D is a regulating factor. Figure 7 represents the SEPIC converter output voltage at starting when PI-controller is used. In this figure, it can be noted that the overshoot is eliminated. Figures 8 and 9 represents the SEPIC converter output voltage and current respectively with load switching. In this figure, the load is changed from 1 kW to be 2 kW when the simulation time beyond 1 second. The load is switched again to be 1 kW when the simulation time is beyond 1.6 seconds. It can be noted that the PI-controller was able to absorb the load changing and fixing the output voltage at its desired value. In this simulation, the proportional gain (KP) was (0.1) and the integral gain (KI) is (4.5).

Single phase inverter fed through a regulated SEPIC converter (Adil Hasan Mahmood)

Figure 8. Output voltage of SEPIC converter with load switching when PI-controller is used

Figure 9. Output current of SEPIC converter with load switching when PI-controller is used

## 4.3. Connecting sepic convertoer to a full-bridge inverter

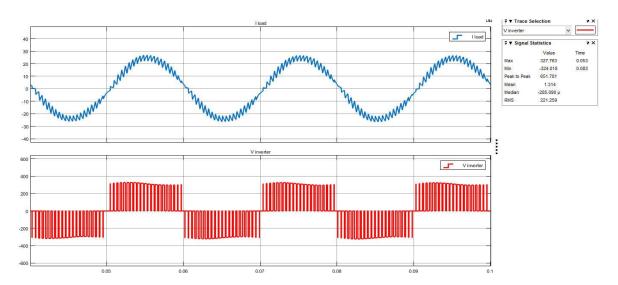

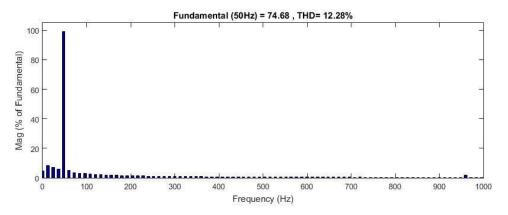

Figure 10 shows AC current and voltage for an R-L load where the RMS output voltage is 230 V. The pulses for the inverter switches are a result of sinusoidal pulse width modulation (SPWM) operation and fed each switch of the inverter [21], [23]-[27]. The modulation index is kept at 0.95. Figure 11 represents the total harmonic distortion for the output voltage value of the inverter which is 12.28%.

Figure 11. THD for the inverter output voltage

## 5. CONCLUSION

A design and simulation of the SEPIC DC/DC converter are made in this paper. In this design, an assumption is made that the change in each inductor current is the same so that the inductance of each coil will be the same. The measured output voltage of the converter is shown at system startup and during load switching. The results showed that a proper controller is needed to regulate the output voltage of the converter. When the converter is connected to a full-bridge inverter, the load has some voltage flickers so, a special filter in the DC and AC sides of the inverter is essentially required. Thus, it can be concluded that this merged system of SEPIC converter and full-bridge inverter is typical for general load applications.

#### REFERENCES

- [1] A. Lachichi, "DC/DC converters for high power application: A survey," 2013 3rd International Conference on Electric Power and Energy Conversion Systems, 2013, pp. 1-4, doi: 10.1109/EPECS.2013.6713026.

- [2] K. V. G. Raghavendra, *et al.*, "A Comprehensive Review of DC-DC Converter Topologies and Modulation Strategies with Recent Advances in Solar Photovoltaic Systems," *Electronics*, vol. 9, no. 1, p. 31, 2020, doi: 10.3390/electronics9010031.

- [3] L. J. Jeremy, C. A. Ooi and J. Teh, "Non-isolated conventional DC-DC converter comparison for a photovoltaic system: A review," *Journal of Renewable and Sustainable Energy*, vol. 12, no. 013502, pp. 1-12, 2020, doi: 10.1063/1.5095811.

- [4] J. Falin, "Designing DC/DC converters based on SEPIC topology," *Analog Applications Journal, Texas Instruments Incorporated*, pp. 19-20, 2008.

- [5] K. B. Nagne and H. K. Naidu, "Comparison of DC-DC Buck Boost and SEPIC Converter for Control of Electronically Commutated BLDC Motor," *International Journal for Innovative Research in Multidisciplinary Field*, vol. 4, no. 5, pp. 1-4, May 2018.

- [6] A. De Nardo, N. Femia, F. Forrisi, M.Granato, "Design of SEPIC with coupled inductors," in *Proc. PCIM Europe*, May 2009, pp. 238-239.

- [7] A. DeNardo, N. Femia, F. Forrisi and M. Granato, "SEPIC converter passive components design," 2008 15th IEEE International Conference on Electronics, Circuits and Systems, 2008, pp. 1002-1005, doi: 10.1109/ICECS.2008.4675025.

- [8] D. Vinodini, S. Hema, S. R. Akshaya and K. Fathima, "Design and Analysis of a SEPIC Converter For PV Applications," ARPN Journal of Engineering and Applied Sciences, vol. 13, no. 24, pp. 9754-9757, 2018.

- [9] T. Bhavin, B. Patel, J. Desai and K. Sonwane, "Analysis of SEPIC Converter," International Journal of Ecology and Development Research (IJEDR), vol. 6, no. 2, pp. 489-494, 2018.

- [10] Geeta and Hemavathi R., "Design and Simulation of Closed Loop SEPIC DC-DC Converter for a Stand-alone Photovoltaic System," *International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering*, vol. 7, no. 10, pp. 1-5, October 2018, doi: 10.15662/IJAREEIE.2018.0710009.

- [11] I. Alhamrouni, M. K. Rahmat, F. A. Ismail, M. Salem, A. Jusoh and T. Sutikno, "Design and development of SEPIC DC-DC boost converter for photovoltaic application," *International Journal of Power Electronics and Drive System* (*IJPEDS*), vol. 10, no. 1, pp. 406-413, March 2019, doi: 10.11591/ijpeds.v10n1.pp406-413.

- [12] R. S. Alishah, M. Y. Hassani, S. H. Hosseini, K. Bertilsson and M. Babalou, "Analysis and Design of a New Extendable SEPIC Converter with High Voltage Gain and Reduced Components for Photovoltaic Applications," 2019 10th International Power Electronics, Drive Systems and Technologies Conference (PEDSTC), 2019, pp. 492-497, doi: 10.1109/PEDSTC.2019.8697249.

- [13] A. Yadav and A. Verma, "Modeling and Analysis of Modified SEPIC Converter Fed by Solar PV System," 2020 2nd International Conference on Advances in Computing, Communication Control and Networking (ICACCCN), 2020, pp. 633-638, doi: 10.1109/ICACCCN51052.2020.9362890.

- [14] H. T. Pathirathne and M. W. P Maduranga, "Design & Simulation of a SEPIC Converter for Home Solar PV Systems," *Conference: 27th IET Annual Technical Conference, At: Colombo, Sri Lanka*, pp. 1-7, October 2020.

- [15] A. Samani and S. Parmar, "Design of SEPIC Converter using MATLAB," International Journal of Innovative Trends in Engineering (IJITE), vol. 13, no. 02, pp. 88-93, 2016.

- [16] M. O. Ali and A. H. Ahmad, "Design, modelling and simulation of controlled sepic DC-DC converter-based genetic algorithm," *International Journal of Power Electronics and Drive Systems (IJPEDS)*, vol. 11, no. 4, pp. 2116-2125, December 2020, doi: 10.11591/ijpeds.v11.i4.pp2116-2125.

- [17] S. I. Khather and M. A. Ibrahim, "Modeling and simulation of SEPIC controlled converter using PID controller," *International Journal of Power Electronics and Drive Systems (IJPEDS)*, vol. 11, no. 2, pp. 833-843, June 2020, doi: 10.11591/ijpeds.v11.i2.pp833-843.

- [18] M. F. Mohammed, A. H. Ahmed and A. T. Humod, "New Switching Technique for the Modified Cascade Five Levels Inverter," ARPN Journal of Engineering and Applied Sciences, vol. 13, no. 14, pp. 4346-4350, July 2018.

- [19] E. H. Aboadla, et al., "A novel optimization harmonic elimination technique for cascaded multilevel inverter," Bulletin of Electrical Engineering and Informatics, vol. 8, no. 2, pp. 405-413, June 2019, doi: 10.11591/eei.v8i2.1500.

- [20] D. R. Vanka and K. C, "Power applications for fuel-cell using switching regulators," *Indonesian Journal of Electrical Engineering and Computer Science (IJEECS)*, vol. 15, no. 1, no. 71-79, July 2019, doi: 10.11591/ijeecs.v15.i1.pp71-79.

- [21] N. F. A. Hamid, M. A. Abd Jalil, N. S. S. Mohamed, "Design and simulation of single phase inverter using SPWM unipolar technique," *Journal of Physics: Conference Series*, vol. 1432, pp. 1-9, 2020.

- [22] F. Haugen, "The Good Gain method for simple experimental tuning of PI controllers," Norwegian Society of Automatic Control, vol. 33, no. 4, pp. 141-151, 2012.

- [23] O. Katsuhiko, "Modern Control Engineering," Prentice Hall Inc., 3rd edition, pp. 669-690, 1997.

- [24] V. A. Kumar and A. Mouttou, "Improved performance with fractional order control for asymmetrical cascaded Hbridge multilevel inverter," *Bulletin of Electrical Engineering and informatics (BEEI)*, vol. 9, no. 4, pp. 1335-1344, August 2020, doi: 10.11591/eei.v9i4.1885.

- [25] S. Siddaraj, U. R. Yaragatti, H. Nagendrappa and V. K. Jhunjhunwala, "Autonomous microgrid based parallel inverters using droop controller for improved power sharing," *Bulletin of Electrical Engineering and Informatics* (*BEEI*), vol. 9, no. 6 pp. 2302-2310, December 2020, doi: 10.11591/eei.v9i6.2663.

- [26] H. Benbouhenni, "A comparison study between fuzzy PWM and SVM inverter in NSMC control of stator active and reactive power control of a DFIG based wind turbine systems," *International Journal of Applied Power Engineering* (*IJAPE*), vol. 8, no. 1, pp. 78-92, April 2019, doi: 10.11591/ijape.v8.i1.pp78-92.

- [27] G. G. Samuel, M. Muthuramaligam, P. S. Manoharan and C. C. A. Rajan, "Control of a stand-alone photovoltaic/battery bank system to supply energy to resistance load," *International Journal of Applied Power Engineering (IJAPE)*, vol. 8, no. 1, pp. 93-100, April 2019, doi: 10.11591/ijape.v8.i1.pp93-100.